## PERFORMANCE ANALYSIS OF FIR FILTER BASED ON MULTIPLE CONSTANT MULTIPLICATION TECHINIQUE WITH **EFFICIENT MULTIPLIER**

**Mr. S.Ramprasad<sup>1</sup>**, **Mr. V. Yuvraj<sup>2</sup>**, <sup>1</sup>Post Graduate Student, <sup>2</sup>Assistant Professor, Department of Electronics and Communication, Dhanalakshmi Srinivasan engineering college, <sup>1</sup>91ramprasad@gmail.com, <sup>2</sup>yuvraj be@yahoo.com.in.

### ABSTRACT

Performance analysis of finite impulse response (FIR) designs are presented by the concept of modified Wallace multipliers .This paper aims at reducing the leakage current, delays and power consumption of Wallace multiplier. This is accomplished by accomplished by modified carry save adder(MCSA). An efficient verilog HDL has been written, successfully simulated and synthesized in Xilinx and the results shows that proposed designs achieve the best area and power than existing system which uses the concept of truncated multiplier.

Index Terms— faithful rounding, finite impulse response (FIR) filters, truncated multipliers, VLSI design.

### **1. INTRODUCTION**

Finite impulse response (FIR) digital filters are one of the most widely used fundamental devices performed in DSP systems, ranging from wireless communications to video and image processing. This paper proposes new parallel FIR filter structures, which are beneficial to symmetric coefficients in terms of the hardware cost, under the condition that the number of taps is a multiple of 2 or 3. The 5 parallel FIR structures gives low area and high speed compare to existing 4 parallel architecture, exploit the inherent nature of symmetric coefficients reducing half the number of multipliers in sub filter section at the expense of additional adders in preprocessing and post processing blocks as in [9]. Exchanging multipliers with adders is advantageous because adders weigh less than multipliers in terms of silicon area. Due to reduction of multipliers, will get low area and high speed fir filter.

The explosive growth of multimedia application, the demand for high-performance and low-power digital signal processing (DSP) is getting higher and higher. The FIR digital filter in [9] is one of the most widely used fundamental devices performed in DSP systems, ranging from wireless communications to video and image processing. Some applications need the FIR filter to operate at high frequencies such as video processing, whereas some other applications request high throughput with a low-power circuit such as multiple-input- multiple-output systems used in cellular wireless communication. Furthermore in[14], when narrow transition band characteristics are required, the much higher order in the FIR filter is unavoidable. Due to its linear increase in the hardware implementation cost brought by the increase in the block size L, the parallel processing technique loses its advantage to be employed in [12]. In a truncated multiplier, several of the least significant columns of bits in the partial product matrix are not formed. This reduces the area and power consumption of the multiplier. It also reduces the delay of the multiplier in many cases, because the modified carry save adder producing the product can be shorter For the Modified Wallace reduction method, once the partial product array (bits) is formed, adjacent rows are collected into nonoverlapping groups of three. Each group of three rows is reduced by Applying a full adder to each column that contains three bits, Applying a half adder to each column that contains two bits, and Passing any single bit columns to the next stage without processing. There are two basic fir structures, direct form and Transposed form as in [8].

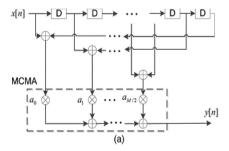

Figure.1(a). Structures of Linear-Phase Even-**Order FIR Filters: Direct Form**

Figure.1(b). Structures of Linear-Phase Even-Order FIR Filters: Transposed Form

# 2. FIR FILTER USING TRUNCATED MULTIPLIER

Truncated multiplier is a good candidate for digital signal processing (DSP) applications including finite impulse response (FIR) and discrete cosine transform (DCT). Through truncated multiplier a significant reduction in Field Programmable Gate Array (FPGA) resources can be achieved as in [6].

Multiplication is frequently required in digital signal processing. Parallel multipliers in [13] provide a high-speed method for multiplication, but require large area for VLSI implementations. In most signal processing applications, a rounded product is desired to avoid growth in word-size. Thus an important design goal is to reduce the area requirements of rounded output multipliers in [14]. The authors present a technique for parallel multiplication which computes the product of two numbers by summing only the most significant columns of the multiplication matrix, along with a correction constant.

A method for selecting the value of the correction constant which minimizes the average and mean square error is introduced. Equations are given for estimating the average, mean square, and maximum error of the rounded product. With this technique, the hardware requirements of the multiplier can be reduced by 25 to 35%, while limiting the maximum error of the rounded product to less than one unit in the last place in [14].

A faithfully rounded truncated multiplier design is presented where the maximum absolute error is guaranteed to be no more than 1 unit of least position. The proposed method jointly considers the deletion, reduction, truncation, and rounding of partial product bits in order to minimize the number of full adders and half adders during tree reduction. Experimental results demonstrate the efficiency of the proposed faithfully truncated multiplier with area saving rates of more than 30%. In addition, the truncated multiplier design also has smaller delay due to the smaller bit width in the final carrypropagate adder in [17].

The standard architecture of  $6\times6$ -bit parallel multiplier, where HA and FA are the half and full adders respectively. It can be expressed by the sum of two segments: the most-significant part MP and the least-significant part LP. The standard  $6\times6$ -bit parallel multiplier can also be divided into three subsets: the most-significant part MP, input correction IC and the least-significant part LP. The fixed width multiplier can be obtained directly by removing the LP region and introducing the IC region to obtain MP' region, which is truncated multiplierin [16].

Multipliers are present in almost all Digital Signal Processing systems. They are area and power demanding structures that constrain the timing and resolution parameters of the entire DSP unit, making the implementation of parallel multipliers desirable to achieve low-power arithmetic systems. Truncated multiplication in [17] reduces the power required by multipliers by only computing the most-significant cant bits of the product However, these results in fixed systems optimized for a given application at design time.

A novel approach to truncation is proposed, where a full precision multiplier is implemented, but the active section of the partial product matrix is selected dynamically at run-time. This allows a power reduction tradeoff against signal degradation which can be modified at any time. Such architecture brings together the power reduction benefits from truncated multipliers and the flexibility of reconfigurable and general purpose devices.

Effective implementation of such a multiplier is presented in a custom dig- ital signal processor, where the concepts of software compensation and multi-level truncation are introduced in [16] and analyzed for different applications. Experimental results are studied, including power measurements from both post-synthesis simulations and a fabricated IC implementation, featuring the rst system-level DSP core using a one-grain programmable truncated multiplier. Fault-tolerant techniques are also studied from an energy efficiency point of view.

The application of such techniques to the proposed DSP architecture shows that, not only energy reductions from both truncated multiplication and fault tolerance can coexist, but the existence of

International Journal of Technology and Engineering System (IJTES) Vol 6. No.1 – Jan-March 2014 Pp. 40-45 ©gopalax Journals, Singapore available at : www.ijcns.com ISSN: 0976-1345

synergies between both techniques to obtain lower energy consumption for DSP architecture.

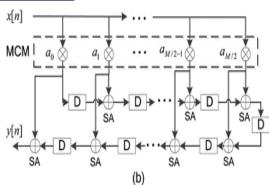

# Figure.2.The architecture of a standard 6×6-bit parallel multiplier

Truncated multipliers offers significant improvements in area, delay, and power. The proposed method finally reduces the number of full adders and half adders during the tree reduction. While using this proposed method experimentally, area can be saved. The output is in the form of LSB and MSB. Finally the LSB part is compressed by using operations such as deletion, reduction, truncation, rounding and final addition. In previous related papers, to reduce the truncation error by adding error compensation circuits. In this project truncation error is not more than 1 ulp (unit of least position). So there is no need of error compensation circuits, and the final output.

Figure.3.The architecture of a truncated 6×6-bit parallel multiplier

#### III. PROPOSED DESIGN OF WALLACE MULTIPLIERS

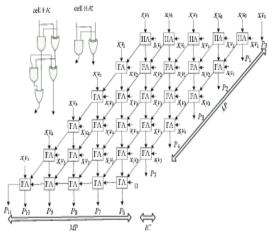

In proposed multiplier, each block addition operation in the column is performed using combination of half adders, full adders, 4:2 compressors and 5:2 compressors instead of full adders and they are selected appropriately based on the number of bits to be added. The first level (Stage A) computation is represented in the fig 1. Thus the generated partial sums are correctly divided and added again in the same manner which forms the second level (stage B) of computation. In the third level (stage C) the final product will arrive only after generated partial sums in the second level are added. The speed has been improved when compared with the truncated design without significantly increasing the amount of power in proposed Wallace Multiplier

In Fig.4 shows the proposed modified Wallace tree multiplier block diagram. The proposed architecture differs from the Wallace multiplier logic represented by dot. 8x8 bit multiplier can be designed similarly by the same method. The Waveform obtained is correctly checked by giving different input bits combinations. The power & delay for both the truncated & proposed Modified Wallace multipliers are compared. A comparison of power & delays are used in proposed and truncated method of 8x8 bits multiplier is given in table1. It is clear from the table that a significant power is reduced in a proposed design. 42.5% power can be saved in a proposed design as compared to truncated design without significant increase in area with a low power technique in 8x8 bit multiplier.

This reduction method is applied to each successive stage until only two rows remain. This process is illustrated by the conventional 8-bit by 8-bit Wallace multiplier shown in Fig.1. The reduction is performed in four stages (each with the delay of one full adder). The third phase will require a (2N-1-S) wide adder, where S – number of stages in reduction.

## Figure.4. Proposed Design for modified Wallace multiplier 8x8

After reducing from 8 stages to 2 stages modified MCSA adder is used to reduce the delay and area. Minimized adder graph (MAG) algorithm consumes more area but multiple constant multiplication algorithms consume less area.

# **3. REDUCED COMPLEXITY WALLACE MULTIPLIER**

It is the modified version of Wallace multiplier. It has less half adders than the normal Wallace multiplier . The partial products are formed by N^2 AND gates. The partial products are arranged in an "inverted triangle" order. The modified Wallace reduction method divides the matrix into three row groups.

1) Use full adders for each group of three bits in a column like the conventional Wallace reduction.

2) A group of two bits in a column is not processed, that is, it is passed on to the next stage (in contrast to conventional method). Single bits are passed on to the next stage as in the conventional Wallace reduction.

3) The only time half adders are used is to ensure that the number of stages does not exceed that of a conventional

#### Modified Carry Save Adder

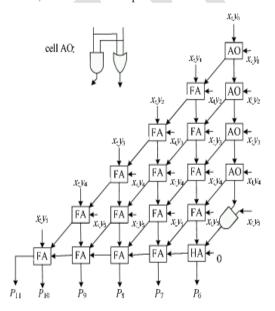

The 16-bit modified CSA Logic Diagram is shown in the Figure 7. It has 17-half adders and 15full adders. Since the ripple carry adder (RCA) is used in the final stage, this structure yields large carry propagation delay. To reduce this delay, the final stage of CSA is divided into 5 groups as shown in Figure 5. The first group includes n  $1+\log_2 n$ -bit

International Journal of Technology and Engineering System (IJTES) Vol 6. No.1 – Jan-March 2014 Pp. 40-45 ©gopalax Journals, Singapore available at : <u>www.ijcns.com</u> ISSN: 0976-1345

> value and other groups includes log<sub>2</sub>n-bit value, where n is the bit size of the adder. The divided groups are listed below, i). {c4,s[4:0]} ii).{c7,x[7:5]}

iii).{c10,x[10:8]} iv).{c13,x[13:11]} v). x[17:14]

### Figure.5. Modified CSA

The first group of output s[4:0] are directly assigned as the final output; the second group  $\{c7,x[7:5]\}$  manipulates the partial result by considering c4 is 0; the third group  $\{c10,x[10:8]\}$ manipulates the partial result by considering c7 is 0; the fourth group  $\{c13,x[13:11]\}$  manipulates the partial result by considering c10 is 0 and the fifth group x[17:14] manipulates the partial result by considering c13 is 0.

Depending on c4 of the first group, the second group mux gives the final result without the carry propagation delay from c4 to c7; depending on c7 of the second group final result, the third group mux gives the final result without the carry propagation delay from c7 to c10; depending on c10 of the third group final result, the fourth group mux gives the final result without the carry propagation delay from c10 to c13 and depending on c13 of the fourth group final result, the fifth group mux gives the final result without the carry propagation delay from c13 to s17.

The main advantage of this logic is that each group computes the partial results in parallel and the muxes are ready to give the final result "immediately" with the minimum delay of the mux. When the Cin of each group arrives, the final result will be determined "immediately". The area indicates the total cell area of the design and the total power is sum of leakage power, internal power, net power and dynamic power. The proposed result shows that the CLA and CSA have reduced area and consume lesser power than MCSA. But the speed of the MCSA architecture has significantly improved and has the

International Journal of Technology and Engineering System (IJTES) Vol 6. No.1 – Jan-March 2014 Pp. 40-45 ©gopalax Journals, Singapore available at : <u>www.ijcns.com</u> ISSN: 0976-1345

least value of power-delay product compared to the conventional CSA and CLA.

| Multiplier                 | Multiplier<br>Delay(ns) | Power(mw) |

|----------------------------|-------------------------|-----------|

| Truncated multiplier       | 27.9                    | 3.9       |

| Wallace Tree<br>multiplier | 25.6                    | 2.7       |

Table 1 Delay And Power Comparison Of 8x8

Multiplier

The comparison table 1 shows the power and delay of both the existing and proposed FIR filter structures. The delay of FIR filter gets increased for lower and reduced statically when go for higher order of FIR filter

### 4. SIMULATION RESULTS

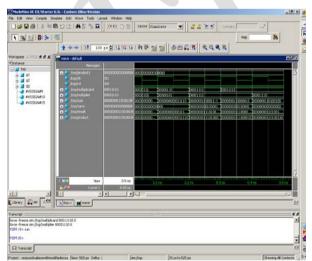

In this work we are evaluating the performance of the proposed FIR filter using low power consumption using Wallace multipliers with modified carry save adders. These multipliers can be implemented using Verilog coding. In order to get the power report and delay report we are synthesizing these multipliers using Xilinx and Modelsim. Simulation result for the FIR filter using modified wallace multiplier are given in figure.

Fig.ure6. Simulation result for the FIR filter using modified wallace

### **5. CONCLUSION**

In this paper, we have proposed design for a FIR filter using Modified Wallace Multiplier with Modified carry save adder. The FIR filter is designed to increase the speed and decrease the power taken by the multiplier unit. Therefore we can conclude that proposed FIR filter design has consumed less power than the Truncated Multiplier design. A tool for generating structural Verilog models of specific instances of these filters is discussed. We have presented a formal synthesis methodology that can be automated and thus it not only ensures formally verified synthesis results but also is very easy to use for end users who do not have any background in formal semantics and reasoning. Our synthesis methodology achieves correctness by construction and thus eliminates the post synthesis verification requirements, which in turn reduces design time. At the end we calculate and compare the power delay product of various adders and multipliers and conclude that for the minimal power design of FIR filter Modified Wallace multiplier using carry save adder is minimum as compare to other adders and multipliers.

#### ACKNOWLEGEMENT

I would like to thank Mr.V.Yuvraj, Assistant professor in Dhanalakshmi Srinivasan College of Engineering and Technology for guiding me to bring this paper successfully.

### REFERENCES

[1] J. G. Chung and K. K. Parhi, "Frequency-spectrum-based low-area low-power parallel FIR filter design," EURASIP J. Appl. Signal Process., vol. 2002, no. 9, pp. 444–453, 2002.

[2] K. K. Parhi, VLSI Digital Signal Processing Systems: Design and Im-plementation . New York: Wiley, 1999.

[3] Z.-J. Mou and P. Duhamel, "Short-length FIR filters and their use in fast nonrecursive filtering," IEEE Trans. Signal Process., vol. 39, no. 6, pp. 1322–1332, Jun. 1991.

[4] J. I. Acha, "Computational structures for fast implementation of L-path and L-block digital filters," IEEE Trans. Circuit Syst., vol. 36, no. 6, pp. 805–812, Jun. 1989.

[5] C. Cheng and K. K. Parhi, "Hardware efficient fast parallel FIR filter structures based on iterated short convolution," IEEE Trans. Circuits Syst. I, Reg. Papers , vol. 51, no. 8, pp. 1492–1500, Aug. 2004.

[6] C. Cheng and K. K. Parhi, "Furthur complexity reduction of parallel FIR filters," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS 2005) ,Kobe, Japan, May 2005.

[7] O. Gustafsson, "Lower bounds for constant multiplication problems," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no. 11, pp. 974–978, Nov. 2007.

[8] Y. Voronenko and M. Puschel, "Multiplierless multiple constant multiplication," ACM Trans. Algorithms, vol. 3, no. 2, pp. 1–38, May 2007.

[9] D. Shi and Y. J. Yu, "Design of linear phase FIR filters with high probability of achieving minimum number of adders," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 58, no. 1, pp. 126–136, Jan. 2011.

[10] R. Huang, C.-H. H. Chang, M. Faust, N. Lotze, and Y. Manoli, "Signextension avoidance and wordlength optimization by positive-offset representation for FIR filter design," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 58, no. 12, pp. 916–920, Oct. 2011.

[11] P. K. Meher, "New approach to look-up-table design and memory-based realization of FIR digital filter," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 3, pp. 592–603, Mar. 2010.

[12] P. K. Meher, S. Candrasekaran, and A. Amira, "FPGA realization of FIR filters by efficient and flexible systolization using distributed arithmetic," IEEE Trans. Signal Process., vol. 56, no. 7, pp. 3009–3017, Jul. 2008.

[13] Deepshikha Bharti , K. Anusudha, "High Speed FIR Filter Based on Truncated Multiplier and Parallel Adder "

International Journal of Engineering Trends and Technology (IJETT) – Volume 5 Number 5 - Nov 2013

[14] S. Karunakaran, Dr. N.Kasthuri,

" Area and Power Efficient VLSI Architecture for FIR Filter using Asynchronous Multiplier, " British Journal of Science 61 December 2011, Vol. 2

[15] Muhammad H. Rais, *member IEEE* "Efficient Hardware Realization of Truncated Multipliers using FPGA " International Journal of Engineering and Applied Sciences 5:2 2009 [16] Shen-Fu Hsiao, Jun-Hong Zhang Jian, and Ming-Chih Chen "Low-Cost FIR Filter Designs Based on Faithfully Rounded Truncated Multiple Constant Multiplication/Accumulation " IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—ii: express briefs, vol. 60, no. 5, may 2013